微電子所研發(fā)出高性能單晶硅溝道3D NOR儲存器

軍工資源網 2022年11月24日NOR閃存以速度快、可靠性高和使用壽命長等優(yōu)勢,在人工智能、汽車電子和工業(yè)領域中發(fā)揮著重要作用。目前,普遍使用的平面NOR閃存在50納米以下技術代的尺寸微縮遇到瓶頸,難以進一步提升集成密度、優(yōu)化器件性能以及降低制造成本。為突破上述瓶頸,科研人員提出多種基于多晶硅溝道的三維NOR(3D NOR)器件,但多晶硅溝道遷移率低、讀取速度慢,影響NOR器件整體性能。

近日,中國科學院微電子研究所集成電路先導工藝研發(fā)中心研究員朱慧瓏團隊利用研發(fā)的垂直晶體管新工藝,制備出高性能的單晶溝道3D NOR閃存器件。該器件上下疊置的晶體管既具單晶硅溝道的高性能優(yōu)勢,又具三維一體集成的制造成本低的優(yōu)點。該器件可在獲得同等或優(yōu)于單晶硅溝道平面NOR閃存器件性能的同時,無需升級光刻機也可大幅提高存儲器集成密度、增加存儲容量。科研團隊研制的3′3′2三維NOR閃存陣列實現了正常讀寫和擦除,達到了讀電流及編程、擦除速度與二維NOR閃存器件相當的目標,且新制程與主流硅基工藝兼容,便于應用。

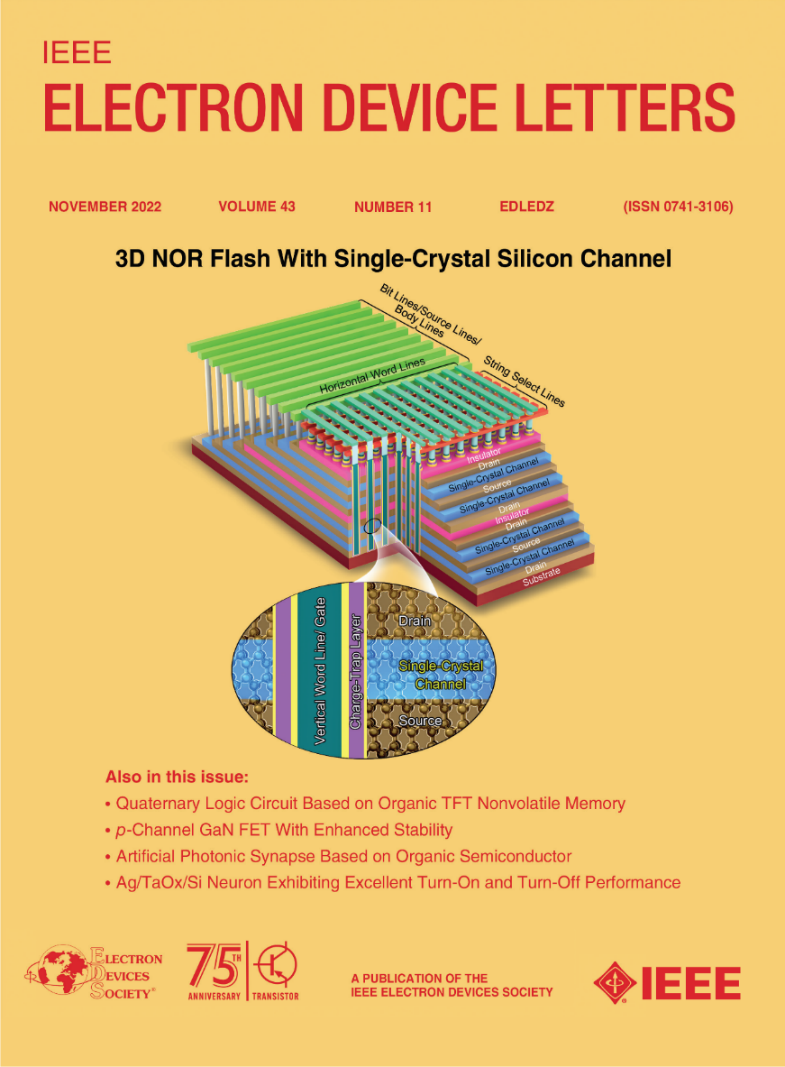

相關研究成果作為封面文章和“編輯特選”(Editors Picks)文章,以A Novel 3D NOR Flash with Single-Crystal Silicon Channel: Devices, Integration, and Architecture為題,發(fā)表在《電子器件快報》(IEEE Electron Device Letters)上。研究工作得到中科院自主部署項目的支持。

圖1.刊登在Electron Device Letters封面上的單晶硅3D NOR電路架構(上)及垂直溝道晶體管結構(下)

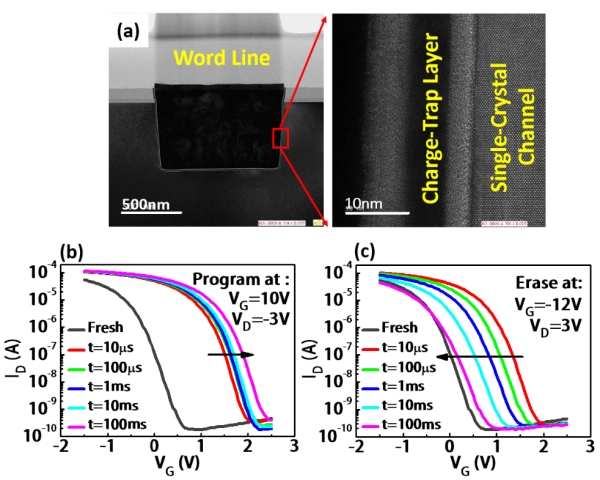

圖2.單晶硅溝道3D NOR器件及電性實驗結果:(a)器件TEM截圖(左)及溝道局部放大圖(右),(b)編程特性,(c)擦除特性